3-269

СООБЩЕНИЯ

ОБЪЕДИНЕННОГО

ИНСТИТУТА

ЯДЕРНЫХ

ИССЛЕДОВАНИЙ

ДУБНА

6/1X-76

10 - 9666

Н.И.Замятин, Д.А.Смолин

БЛОКИ БУФЕРНОЙ ПАМЯТИ В СТАНДАРТЕ КАМАК

1976

Н.И.Замятин, Д.А.Смолин

БЛОКИ БУФЕРНОЙ ПАМЯТИ В СТАНДАРТЕ КАМАК

При проведении измерений на физических установках часто встречаются задачи, выполняя которые необходимо иметь возможность быстрого сбора цифровой информации (с аналого-цифровых преобразователей, счетчиков), ее хранения и выдачи в ЭВМ. Эта задача легко решается с помощью блоков буферной памяти. В Отделе новых методов ускорения были разработаны блоки памяти, которые использовались в системе измерений для определения параметров электронного пучка на радиусе инжекции. Информация с датчиков обрабатывалась АЦП и в цифровом бинарном коде переписывалась в буферную память, из которой в промежутках времени между циклами ускорителя считывалась в ЭВМ. Объем буферной памяти 32 слова х 16 бит был достаточен, кроме того, была предусмотрена возможность последовательно нарашивать число аналогичных блоков памяти.

## І. БЛОК БУФЕРНОЙ ПАМЯТИ БП-021 С НАКОПИТЕЛЕМ НА МОП - ИНТЕГРАЛЬНЫХ МАТРИЦАХ 1ЯМ3

Блок памяти выполнен в стандарте КАМАК-"Вишня". Размер передней панели 2М, на ней расположены:

- а) BP-1 коаксиальный разъем типа CP-50-74Ф с обозначением "Strobe" вход внешнего сигнала "разрешение записи";

- б) ВР-2 коакснальный разъем типа СР-50-74Ф

с обозначением "Clear" вход внешнего сигнала "очистка памяти";

в) KH-1 - кнопочный микропереключатель с обозначением "Reset" - "очистка памяти".

Задняя панель блока содержит два разъема типа 2РМ-32Ш. Наличие двух разъемов дает возможность вести запись с двух источников информации. Причем информация должна подаваться на разъемы одновременно, так как запись происходит по одному сигналу "Strobe". При записи с двух разъемов - слова 8-разрядые, слово с первого источника информации занимает разряды 1-8, слово со второго источника - разряды 9-16.

При работе с одним источником информации запись ведется 16-разрядными словами. Для контроля работоспособности блока предусмотрена возможность записи с W-шин по команле KAMAK.

# 1.1. Технические характеристики блока БП-021

### Входы

- а) на вход внешнего сигнала "Strobe" подаются импульсы с уровнями TTL на несогласованную нагрузку. Длительность сигнала "Strobe" ≥ 0,3 мкс, минимальный период следования импульсов записи равен 1,0 мкс;

- б) на вход "Clear" подаются импульсы с уровнями TTL и длительностью > 100 нс;

- в) на внешние разъемы записи 2РМ-32Ш поступают импульсные сигналы информации с уровнями TTL одновременно с сигналом "Strobe".

#### Объем накопителя

Объем накопителя Q=512 бит (32 слова х 16 разрядов), запись и считывание информации 16-разрядными словами, код бинарный.

## Использование функций КАМАК

а) запись по командам КАМАК в 32 адреса: 1-е слово - N·A(0)·F(16)·S<sub>1</sub>, 2-е слово - N·A(1)·F(16)·S<sub>1</sub>, 16-е слово -  $N \cdot A(15) \cdot F(16) \cdot S_1$ , (Q=1) 17-е слово -  $N \cdot A(0) \cdot F(17) \cdot S_1$ ,

32-е слово -  $N \cdot A(15) \cdot F(17) \cdot S_1$ .

б) Чтение информации 16-разрядными словами без разрушения информации:

1-е слово - N·A(0)·F(0), 2-е слово - N·A(1)·F(0), 16-е слово · N·A(15)·F(0), 17-е слово - N·A(0)·F(1),

32-е слово - N·A(15)·F(1).

- в) Общая очистка памяти по команде:  $N \cdot A(0) \cdot F(9) \cdot S_{2}$ , (Q=0).

- r) Обшие сигналы управления (Z+C)·S<sub>2</sub> производят очистку накопителя и сброс всех триггеров блока. Сигнал "Inhibit" запрешает запись по внешнему сигналу "Strobe".

Потребление по цепи постоянного тока

+6 B - 0,8 A,

-6 B - 0,64 A,

+12 B - 0,6 A, -12 B - 0,03 A.

Детали блока занимают две стандартные платы.

# Блок-схема буферной намяти БП-021

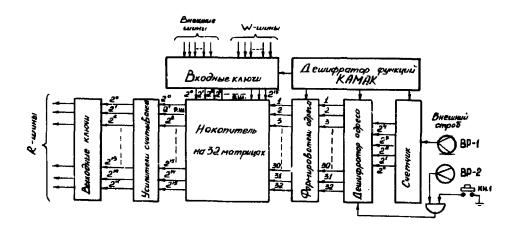

На рис. 1 приведена блок-схема памяти, где показаны основные узлы устройства.

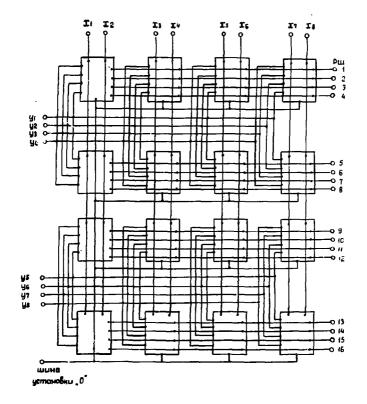

Накопитель блока БП-021

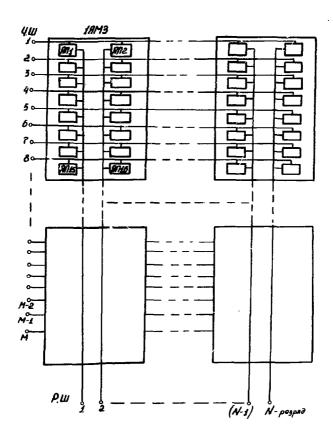

Накопитель построен на 32 МОП-матрицах памяти 1ЯМЗ. Микросхема 1ЯМЗ представляет собой интегральную магрицу памяти с информационной емкостью 16 двоичных единиц (8 слов х 2 разряда). На рис. 2

Рис. 1. Блок-схема буферной памяти БП-021.

Рис. 2. Организация накопителя на элементах 1ЯМ3.

показана организация накопителя емкостью  $Q = M \cdot N$ , где M - число адресов, N - число разрядов. Для блока  $E\Pi - 021$  M = 32 адреса, N = 16 разрядов и  $Q = 32 \times 16 = 512$  бит.

Выводы "подложка" всех матриц объединены с общей шиной. Питание матриц общее и равно  $E_n=+6,5$  В, максимальный ток по цепи питания матриц равен  $5\,\mathrm{mA}$  в режиме чтения, если во всех 16 разрядах записаны "1".

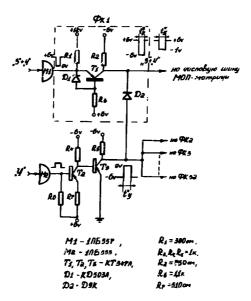

Формирователи адреса необходимы для формирования на числовых шинах (Ч.Ш.) накспителя сигналов "чтение" и "запись". Схема одного формирователя приведена на рис. 3, всего необходимо иметь 32 формирующих каскада (Ф.К.), так как накопитель имеет 32 независимых

Рис. 3. Формирователь адреса.

числовых шины. Формирователь состоит из элементов  $T_1$ ,  $R_1$ ,  $R_2$ ,  $R_3$ ,  $D_1$ ,  $D_2$ . Транзистор  $T_1$  включен по схеме с общей базой, диод  $D_1$  необходим для защиты эмиттерного перехода от обратного напряжения. Величина  $R_1$  выбиреется исходя из нагрузочной способности микросхемы M1. Величина  $R_2$  выбирается с учетом допустимого тока через  $T_1$ ; чем меньше  $R_2$ , тем лучше фронты сигналов управления на  $\Psi$ .Ш. и, следовательно, выше быстродействие устройства.

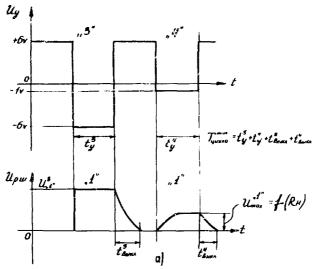

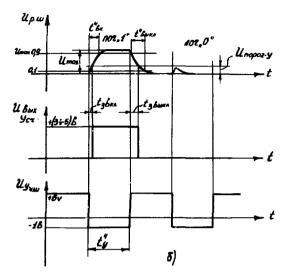

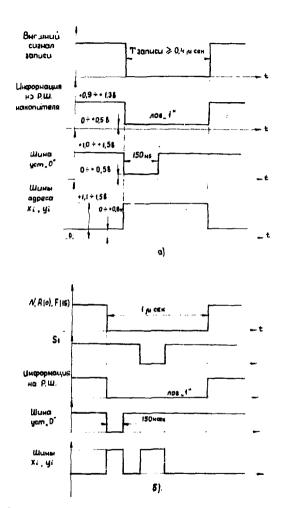

Схема на транзисторах  $T_2$  и  $T_3$  является общей для всех 32 формирователей адреса и предназначена для формирования сигнала положительной полярности в режиме чтения, ограничивающего амплитуду отрицательного управляющего сигнала на ЧШ.В режиме записи эта схема развязана с формирователями через диоды (с Ф.К. — через  $D_2$ ). Временная диаграмма полного цикла "запись-"чтение" показана на рис. 4а.

Рис. 4а. Временная диаграмма в режиме чтения без разрушения информации.

Дешифратор адреса имеет 32 выхода, с которых подаются сигналы адреса на входы формирователей по командам "запись" или "чтение" с использованием функций КАМАК и в режиме "запись по внешнему стробу".

Счетчик необходим для выбора адреса при записи информации по внешнему стробу, пять разрядов счетчика обеспечивают дешифрацию 32 адресов.

Усилитель считывания информации с разрядных шин накопителя выполнен на микросхемах К1УТ221В. На каждую разрядную шину необходим один усилитель, всего 16 микросхем. Выходы усилителей К1УТ221В согласованы со входами выходных ключей на ТТL- схемах. Выходные ключи формируют на R-шинах сигналы в режиме чтения.

Входные ключи управляют записью информации как с внешних разъемов 2РМ, так и с W -шин магистрали. Кроме того, входные ключи формируют необходимые уровни на разрядных шинах накопителя при записи логических "0" или "1".

Так как информация записывается и считывается по общей разрядной шине (РШ), то к устройству записичтения предъявляются следующие требования:

а) В режиме "запись" на РШ должнь присутствовать сигналы с амплитудой для лог. "1"  $U_{p,m}$  = 5 + 6,5 B, для лог. "0"  $U_{n,m}$  = 0 + 2 B;

сигналы на РШ должны быть длительностью не меньше, чем сигналы на числовой шине.

б) В режиме "чтение" устройство записи-чтения не должно влиять на величину нагрузки разрядной шины

$R_{\rm H}$ ; ток считывания из ЯП в разрядной шине, нагруженной на сопротивление  $R_{\rm H}=7,5$  кОм, и при амплитуде сигнала "чтение" на ЧШ -1 В равен:

$$I_{C4}^{1} = 200 \text{ MKA},$$

$I_{C4}^{0} = 0 + 7 \text{ MKA}.$

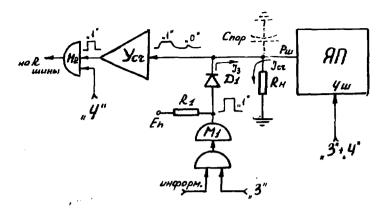

На рис. 5 приведена схема устройства записи-чтения. Запись информации происходит с помощью микросхемы с открытым коллектором  $M_1$ , диода  $D_1$  и сопротивле-

Рис. 46. Временная диаграмма цикла запись "1" - чтение "1".

ния  $R_1$  ( $M_1$  - 1ЛБ558,  $D_1$  - ГД508,  $R_1$  = 380 Ом). Амплитуда сигнала записи  $U_3^1$  лог. "1" на РШ будет отличаться от  $E_n$  = +6 B на величину, равную падению напряжения на диоде  $D_1$  и сопротивлении  $R_1$ . Кроме того, при записи "1" будет затягивание заднего фронта сигнала на РШ на время, равное  $t_{B \text{ыкл.}}^3$ , — это время выключения диода  $D_1$  и разряда Спар. через сопротивление  $R_1 || R_{\text{BX.y}}$ , где  $R_{\text{BX.y}}$  — входное сопротивление усилителя считывания, Спар. — паразитная емкость на разрядной шине.

При считывании информации из ЯП диод  $D_1$  исключает влияние  $R_1$  и  $M_1$  (на выходе  $M_1$  в режиме "чтение" присутствует низкий потенциал). Нагрузкой для ЯП при чтении будет сопротивление, равное ( $R_H \mid\mid R_{\rm BX,V}$ ).

Рис. 5. Устройство записи-чтения.

При считывании сигнал на РШ имеет форму, показанную на рис. 46. Время включения  $\mathfrak{t}_{BKJ}^{\mathfrak{q}}$  определяется временем включения управляющего элемента ЯП. Время выключения  $\mathfrak{t}_{BbKJ}^{\mathfrak{q}}$ , определяется разрядом  $\mathfrak{C}_{\Pi ap}$ , через сопротивление  $\mathfrak{R}_{\mathfrak{q}}$   $||\mathfrak{R}_{BX,\mathbf{v}}||$ .

Минимальное время полного цикла (запись-чтение) можно записать в виде

$$T_{II} = t_y^4 + t_{BHKJ}^4 + t_y^3 + t_{BHKJ}^3,$$

где  $\mathbf{t}_{\mathbf{y}_3}^{\mathbf{q}}$  - длительность сигнала адреса на ЧШ при чтении,  $\mathbf{t}_{\mathbf{y}}^{\mathbf{q}}$  - длительность сигнала адреса при записи,  $\mathbf{t}_{\mathrm{BЫКЛ}}^{\mathbf{q}}$  - время выключения при чтении "1",  $\mathbf{t}_{\mathrm{BЫКЛ}}^{\mathbf{q}}$  - время выключения при записи "1".

Время полного цикла работы для данного элемента памяти определяется в основном двумя временами,  $t_y^3$  и  $t_{Bыкл}$ . Величину  $t_y^4$  можно брать минимальной, исходя из условия  $t_y^4 \ge t_{3,Bkл}$ .  $t_{3,Bkn}$ . – задержка

усиленного сигнала  $\mathbf{U}_{\mathrm{Bbix},\mathbf{y},\mathrm{cq}}$  относительно сигнала управления  $\mathbf{t}_{\mathbf{y}}^{\mathbf{q}}$  .

Типичные значения времен для БП-021 следующие:

$$t_y^3 \ge 300$$

не;  $t_{\rm Bbikn.}^3 = 600$  не;  $t_y^4 \ge 200$  не;  $t_{\rm Bbikn.}^4 = 200$  не;  $t_{\rm 3.Bkn.}^4 = 200$  не; для значений:  $U_{\rm порог.y} = +0.6$  В,  $R_{\rm H} = 7.5$  К,  $U_{\rm Walls} = -1$  В,

где  $U_{\text{порог.y-}}$  порог усилителя чтения,  $U_{\text{ч.ш.}}$  – амплитуда управляющего сигнала на числовой шине при чтении.

Из вышесказанного видно, что минимальное время цикла памяти ограничено быстродействием самой микросхемы ( $t_y^3$  и  $t_y^4$ ) и параметрами внешнего устройства записи-чтения ( $t_{\rm Bыкл_*}$ ,  $t_{\rm Bыкл_*}$ ).

## II. БЛОК БУФЕРНОЙ ПАМЯТИ (БП-061) С НАКОПИТЕЛЕМ НА ЭЛЕМЕНТАХ ПАМЯТИ СЕРИИ 141

Елок выполнен в стандарте КАМАК. Размер передней панели блока - 2M, на ней расположены:

- а) разъем типа РПМ-7-36Ш для записи информации;

- б) ВР-1 коаксиальный разъем с обозначением

- "Strobe" вход внешнего сигнала "разрешение записи";

- в) ВР-2 коаксиальный разъем с обозначением

- "Exp." выход для разрешения записи в другой блок памяти при наращивании ее объема;

- r) BP-3 разъем с обозначением "Clear" вход для внешнего сигнала "очистка памяти":

- д) BP-4 разъем с обозначением "Stop" выход сигнала, формируемого при обращении к последнему адресу накопителя памяти:

- е) КН-1 микропереключатель с обозначением "Reset" очистка всей памяти. Все коаксиальные разъемы-типа LEMO. Задняя панель блока содержит:

- а)  $\Pi 1$  переключатель с обозначением  $\frac{32/10}{64/8}$  переключатель режима записи через разъем РПМ-7-36Ш;

б) разъем платы с соединениями типа КАМАК.

### II.1. Технические характеристики блока

#### Входы

- а) На вход внешнего сигнала "разрешение записи" "Strobe" подаются импульсы с уровнями TTL на несогласованную нагрузку. Длительность сигнала "Strobe" ≥ 0,4 мкс; минимальный период следования 0,5 мкс.

- 6) На внешний разъем записи РПМ-7-36Ш подаются импульсные сигналы информации с уровнями TTL одновременно с сыгналом "Strobe" и длительностью > 0,4 мкс.

- в) На вход "Clear" подаются импульсы с уровнями TTL и длительностью ≥100 нс.

#### Выходы

- а) выход с обозначениями "Exp." импульсные сигналы с уровнями TTL, повторяющье по длительности сигналы "Strobe";

- б) выход с обозначениями "Stop" -импульсные сигналы с уровнями TTL длительностью 1 мкс.

### Объем накопителя блока памяти

Накопитель построен на запоминающих матрицах К1ЯМ411. Объем Q = 512 бит, через внешний разъем РПМ можно записать 32 слова по 16 разрядов или 64 слова по 8 разрядов. Считывание информации из блока без разрешения информации.

Использование функций КАМАК

$$N \cdot A(0) \cdot F(0)$$

- команда чтения информации из блока памяти. Для опроса всего  $Q = 1$  накопителя необходимо генерировать 32 раза команду чтения, предварительно установив счетчик

адреса в ноль. N·A(0)·F(16)·S1 - запись информации с ₩-шин

(Q=1, X=1) 16-разрядными словами. N·A(0)·F(11)·S2 - установка в ноль счетчика адреса. (Q=0, X=1).

N.A(0).F(9).S2 - очистка накопителя 3У и сброс (Q=0,X=1). всех триггеров устройства в ноль.

Общие сигналы управления (Z+ C)·S2 производят очистку накопителя ЗУ и сброс триггеров.

Потребление по цепи постоянного тока

+6 B - 1,2 A,

-6 B - 0.1 A.

Все детали схемы размещены на одной стандартной плате КАМАК.

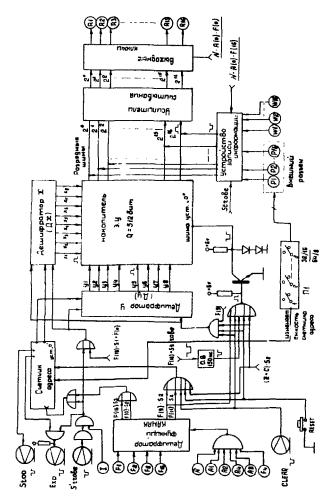

# II.2. <u>Функциональная схема БП-061</u>

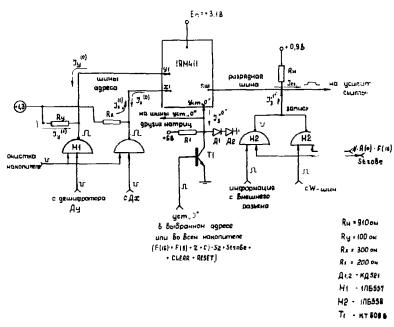

На рис. 6 приведена функциональная схема блока БП-061.

Накопитель блока БП-061

Накопитель памяти емкостью 512 бит построен на 16 интегральных схемах К1ЯМ411. Организация накопителя показана на рис. 7.

При записи 8-разрядными словами (режим записи 64/8) условие выбора одного адреса накопителя можно записать в виде

$$X_i \cdot Y_k = 1$$

,  $(i = 1, 2, ..., 8; k = 1, 2, ..., 8)$ ,

Рис. 6. Функциональная схема буферной памяти БП-061.

Рис. 7. Организация накопителя на элементах памяти 19M411.

где  $X_i$  и  $Y_k$  — шины адреса накопителя, объединяющие X- и Y —шины магриц памяти. Сумма всевоэможных комбинаций  $X_i \cdot Y_k = 1$  определяет количество слов накопителя и равна 8x8=64 слова по 8 разрядов. В режиме записи 64/8 разрядные шины (РШ) накопителя попарно объединяются: (РШ1 х РШ9), (РШ2 х РШ10),... (РШ8 х РШ16). Считывание информации из накопителя идет только 16-разрядными словами, причем в первых восьми разрядах (1-8) будет информация записанных нечетных адресов (A1,A3,...,A63), а в старших разрядах (9-16)—информация четкых записанных адресов (A2,A4,...,A64). В таблице 1 моказан выбор адресов в накопителе в режиме 64/8. При записи 8-разрядными словами увеличивается словарный объем памяти в 2 раза по сревнению с записью 16-разрядными словами

Таблица 1

| Запись 64/8                                                                               | Чтение 32/16                                                                                                                                                      |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-е слово - A1=X1·Y1,<br>2-е слово - A2=X1·Y5,                                            | 1-е слово- A1=X1·Y1·Y5,                                                                                                                                           |

| 7-е слово - A7 = X1 · Y4,<br>8-е слово - A8 = X1 · Y8,<br>9-е слово - A9 = X2 · Y1,       | 4-е слово - A4=X1·Y4·Y8,<br>5-е слово - A5-X2·Y1·Y5,                                                                                                              |

| 10-е слово - A10 = X2 · Y5,<br>31-е слово - A31 = X4 · Y4,<br>32-е слово - A32 = X4 · Y8, | $\frac{16-e \text{ слово} - \text{A16} = \text{X4} \cdot \text{Y4} \cdot \text{Y8}}{17-e \text{ слово} - \text{A17} = \text{X5} \cdot \text{Y1} \cdot \text{Y5}}$ |

| 33-е слово - A33 = X5 · Y1,<br>34-е слово - A34 = X5 · Y5,                                | 32-е слово - A32=X8·Y4·Y8.                                                                                                                                        |

| 63-е слово - A63 = X8·Y4,<br>64-е слово - A64 = X8·Y8.                                    |                                                                                                                                                                   |

Запись 16-разрядными словами может вестись как с внешнего разъема, так и с шин магистрали  $\Psi$ .

| Запись 32/16                                                         | Чтение 32/16                                          |

|----------------------------------------------------------------------|-------------------------------------------------------|

| 1-е слово - A1 =X1.Y1.Y5,<br>2-е слово - A2= X1.Y2.Y6,               | 1-е слово - A1=X1·Y1·Y5,<br>2-е слово - A2=X1·Y2·Y6,  |

| 4-е слово - A4=X1 ·Y4·Y8,<br>5-е слово - A5=X2·Y1·Y5,                | 4-е слово - A4=X 1·Y4·Y6,<br>5-е слово - A5=X2·Y1·Y5, |

| 8-е слово - A8= X2·Y4·Y8,<br>9-е слово - A9= X3·Y1·Y5,               |                                                       |

| 31-е слово - A31 = X8 · Y3 · Y7,<br>32-е слово - A32 = X8 · Y4 · Y8. | · · · · · · · · · · · · · · · · · · ·                 |

Как показано на рис. 6, шина установки нуля является общей для всех матриц памяти. В начале каждого цикла записи на шину установки "0" подается импульс длительностью 150 нс, этот сигнал необходим для предварительной установки нулей во всех разрядах выбранного адреса накопителя. При такой организации цикла записи нет необходимости делать общую очистку накопителя после считывания информации. На рис. 8 (а,б) показаны временные диаграммы сигналов на шинах накопителя в режиме записи с внешнего разъема и в режиме КАМАК. Питание матриц общее и равно Еп = +3,1 В±10%, потребление матриц максимальное в режиме хранения информации и составляет 0,5 А.

## Дешифратор адреса

Дешифратор адреса необходим для выбора одного из адресов накопителя и сопряжения уровней TTL с уровнями на адресных шинах X и Y. Дешифратор адреса состоит из двух дешифраторов:  $D_x$  (координата X) и  $D_y$  (координата Y). На входы дешифраторов  $D_x$  и  $D_y$  подаются сигналы с триггеров счетчика адреса, которые стробируются командами  $KAMAK - N \cdot A(0)$  ( $F(0) + F(16) \cdot SI$ ) или внешним сигналом записи "Strobe". В качестве элементов сопряжения TTL -уровней с уровнями на адресных шинах X и Y исполь-

Рис. 8. Временные диаграммы работы накопителя: а) при записи с внешнего разъема РПМ-7-36Ш, б) при записи по команде КАМАК.

зуются микросхемы с открытым выходом 1ЛБ557, внешние сопротивления которых подсоединяются к питанию +1,3В  $M_1$ , рис. 9. Сопротивления  $R_x$  и  $R_y$  выбираются исходя из допустимых токов через 1ЛБ557 и токов по шикам X и Y.

$$I_{x}^{0} \le 34 \text{ MA};$$

$I_{x}^{1} \le 0.4 \text{ MA};$   $I_{y}^{0} \le 36 \text{ MA};$   $I_{y}^{1} \le 1.2 \text{ MA};$

где  $I_x^0$  ,  $I_y^0$  и  $I_x^1$  ,  $I_y^1$  — токи в адресных шинах X,Y накопителя при логических "0" и "1" соответственно. К одной шине X накопителя подсоединены шины четырех матриц и к одной шине Y накопителя — шины восьми микросхем (рис. 7).

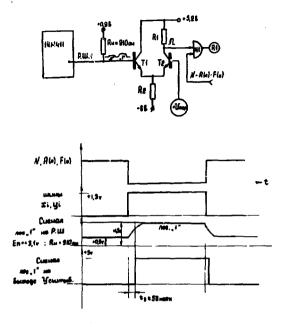

Рис. 9. Схема включения элемента памяти 1ЯМ411 в блоке БП-061.

### Счетчик адреса

Счетчик адреса необходим для последовательной выборки адресов накопителя в режимах записи и чтения.

При записи с внешнего разъема РПМ-7-36Ш состояние счетчика меняется по заднему фронту сигнала "Strobe". После записи информации в последний адрес накопителя (в режиме 64/8 – это 64-й адрес; в режиме 32/16 – 32-й адрес) вырабатывается сигнал "Stop", запрешающий доступ к накопителю по сигналам "Strobe". Чтобы считать записанную информацию из накопителя, необходимо счетчик адреса поставить в "0" по команде N·A(0)·F(11)·S2. Предусмотрена возможность наращивания объема памяти с использованием аналогичных блоков памяти БП-061. При этом внешний сигнал записи "Strobe" подается на БП-061, в который записываются первые слова, а сигналы с выхода "Exp. "первого блока подаются навход "Strobe" следующего БП-061 после переполнения первого блока.

При работе БП-061 в режиме КАМАК счетчик адреса считает сигналы:

- а) при записи N·A(0)·F(16)·S2,

- б) при чтении N·A(0)·F(0)·S2.

Переключатель режима записи с внешнего разъема П1 управляет работой счетчика – увеличивает емкость счетчика на один разряд при записи 64/8, в режимах работы КАМАК переключатель П1 не влияет на работу блока. Счетчик адреса устанавливается в "0" по командам:  $N\cdot A(0)[\ F(9)+F(11)]\cdot S2$  и по сигналам:  $(Z+C)\cdot S2$ , Clear, Reset.

### Усилители считывания

На рис. 10 приведена схема усилителя чтения ( $T_1$ ,  $T_2$  - KT315,  $R_1$  = 1 кОм,  $R_2$  = 910 Ом, Unopor. = = +1,3 В, такой усилитель необходим для каждой разрядной шины накопителя. На вход усилителя поступает сигнал с разрядной шины (РШ), нагруженной на  $R_H$ . Величина порога усилителя выбирается исходя из амплитуд сигналов чтения на РШ и "0" и "1", т.е.  $U_q^0 < U_{nopor}.< U_q^1$ .

Рис. 10. Усилитель считывания с разрядной шины накопителя и временная диаграмма при чтении.

Сигнал положительной поларности "1" с уровнями TTL снимается с выхода усилителя и подается на выходные ключи, где стробируется командой чтения  $N \cdot A(0) \cdot F(0)$ .

# Устройство записи

У тройство записи выполняет функцию согласования TTL — уровней с уровнями, необходимыми для записи "0" и "1" по разрядным шинам накопителя, а также дает возможность вести запись в режимах:

- а) с W шины 16-разрядными словами.

- б) с разъема РПМ 8-разрядными словами,

- в) с разъема РПМ 16-разрядными словами.

На рис. 9 показана схема записи по одной РШ накопителя ( $M_2$  ,  $T_1$  ,  $R_1$  ,  $D_1$  ,  $D_2$  ,  $R_{_{\rm H}}$  ). Ток по шине "установка "0"" равен:

- а) 4.5 мА при установке "0" по одному адресу;

- б) 144 мА при общей очистке накопителя.

В заключение авторы считают своим долгом выразить благодарность И.М.Мельниченко, Н.Н.Шербакову, В.И.Гурскому за изготовление блоков.

### ЛИТЕРАТУРА

- 1. Т.В.Беспалова, И.А.Голутвин, В.М.Головин и др. Установка для исследования поведения электронного пучка в адгезаторе коллективного ускорителя, работающая на линии с ЭВМ. Труды VII Международного симпозиума ОИЯИ по ядерной электронике, Будапешт, 1973 г. ОИЯИ, Д13-7616, Дубна, 1974.

- 2. П.А.Голутвин, Н.П.Замятин, В.Д.Кондрашов и др. Аналоговые и дискретные блоки, выполненные в стандарте КАМАК. Труды VII Международного симпозиума ОИЯП по ядерной электронике, Будапешт, 1973 г. ОИЯП, Д13-7616, Дубна, 1974.

Рукопись поступила в издательский отдел 31 марта 1976 года.